### UNIVERSIDADE FEDERAL DE SANTA CATARINA PROGRAMA DE PÓS-GRADUAÇÃO EM ENGENHARIA ELÉTRICA

### Rodrigo Eduardo Rottava

### ANALYSIS AND DESIGN OF A CMOS DLL-BASED CONDITIONER FOR A SAW-DL RELATIVE HUMIDITY SENSOR

Master dissertation submited to the Programa de Pós-Graduação em Engenharia Elétrica da Universidade Federal de Santa Catarina in order to obtain the degree of Master of Electrical Engineering. Advisor: Prof. Dr. Fernando Rangel de

Sousa

Co-advisor: Dr. Sergey Balashov

Florianópolis

2017

# Ficha de identificação da obra elaborada pelo autor, através do Programa de Geração Automática da Biblioteca Universitária da UFSC.

Rottava, Rodrigo

Analysis and Design of a CMOS DLL-Based

Conditioner for a SAW-DL Relative Humidity Sensor /

Rodrigo Rottava; orientador, Fernando Rangel de

Sousa, coorientador, Sergey Balashov, 2017.

124 p.

Tese (doutorado) - Universidade Federal de Santa Catarina, Centro Tecnológico, Programa de Pós Graduação em Engenharia Elétrica, Florianópolis, 2017.

Inclui referências.

1. Engenharia Elétrica. 2. Sensor SAW. 3. Delay Locked Loop. 4. Umidade Relativa. 5. CMOS. I. Rangel de Sousa, Fernando. II. Balashov, Sergey. III. Balashov, Sergey. IV. Universidade Federal de Santa Catarina. Programa de Pós-Graduação em Engenharia Elétrica. V. Título.

# Rodrigo Eduardo Rottava

# ANALYSIS AND DESIGN OF A CMOS DLL-BASED CONDITIONER FOR A SAW-DL RELATIVE HUMIDITY SENSOR

This dissertation was accepted in its present form by the Programa de Pós-Graduação em Engenharia Elétrica as a partial fulfillment of the requirements for obtaining the degree of Master in Electrical Engineering. Florianópolis, 25/08/2017.

Marcelo Lobo Heldwein, Dr. Graduate Program Coordinator

Master's Committee:

Daniel Pagano, Dr. UFSC

Paulo Augusto Dal Eabbro, Dr., Chipus

Sandro Binsfeld Ferreira, Dr., Unisinos

### AGRADECIMENTOS

Ao meu pai, Marcos, às minhas duas mães, Cleudenice e Marilene, e às minhas quatro irmãs, por todo o amor, suporte e confiança, e por me apoiarem nos momentos difíceis.

Aos meus bons amigos, os quais tenho a graça de ter ao meu lado tanto nos momentos bons quanto nos ruins.

Ao meu orientador, Prof. Fernando Rangel de Sousa, por me instigar a pensar de forma criativa, por sempre ter um minuto, que comumente se torna mais de uma hora, para me orientar, e por me fazer ir além dos limites dos livros e artigos.

Ao meu coorientador, Prof. Sergey Balashov, por toda a orientação e discussões técnicas que possibilitaram que este trabalho tomasse forma.

Aos meus colegas de laboratório, por me ajudarem a solucionar problemas e pelas longas conversas nos almoços e jantares. Agradecimento especial a Rodrigo Pereira pela ajuda com FPGA, a Maicon Pereira pela ajuda com USRP e a Roddy Romero pela ajuda com USRP e por preparar as soluções salinas utilizadas nas medições do sistema.

A Nycollas Ferraz, por todo o suporte e paciência nos meses que antecederam a defesa, sem dúvidas os mais difíceis.

À Universidade Federal de Santa Catarina, ao CNPq, e acima de tudo ao povo brasileiro, por financiarem tanto esta pesquisa como a minha formação acadêmica.

### ABSTRACT

Surface acoustic wave sensors are electromechanical structures that can be used to transduce a great variety of physical, chemical, and biological quantities into electrical quantities. The measurand interacts with the surface, usually coated with a special sensitive layer, causing variations in the energy and phase-velocity of the traveling mechanical wave. These devices behave like delay lines or resonators, altering the characteristics (phase and amplitude) of the electric signal applied to it as a function of the measurand. In the literature, these sensors are reported with high responsivity, fast response time, small size, and reasonable cost. However, the conditioners generally used to process the SAW sensor signals require large and expensive measurement equipments such as vector network analyzers, spectrum analyzer, or frequency counters. In this work, we present a novel conditioner for SAW delay line sensors. This conditioner avoid the use of such equipments, because it directly converts the measurand into a digital word. A fully-digital Delay-Locked Loop is used to measure delay variations in the signal transpassing the SAW delay line sensor. As a case study we designed an integrated circuit prototype to condition a SAW humidity sensor. The conditioner was fabricated in technology GF CMOS 130 nm, and occupies an area of 0.433 mm<sup>2</sup>. Except for two comparators, the integrated circuit is entirely composed of standard logic circuits. This conditioner was tested stand-alone and in the proposed setup to measure relative humidity. Four saturated saline solutions were used to create four environments with specific relative humidities in the range from 32.8 to 90 %. The setup was tested in these four RH points, and the results show four distinguishable levels in the conditioner response. These results were replicated several times with a fair reproducibility. Based on these measurements, we were able to demonstrate the correct operation of the novel conditioner for SAW-DL sensors proposed in this work.

Keywords: SAW sensor, Delay-Locked Loop, relative humidity, CMOS.

### RESUMO

Sensores por onda acústica de superfície são estruturas eletromecânicas que podem ser utilizadas na transdução de uma ampla variedade de grandezas físicas, químicas, e biológicas para variáveis elétricas. grandeza a ser convertida interage com a superfície, usualmente coberta com um filme sensível, causando variações na energia e velocidade de fase da onda mecânica. Estes dispositivos se comportam como linhas de atraso ou ressonadores, alterando as características (fase e amplitude) do sinal elétrico aplicado em função da grandeza. Na literatura, estes sensores são reportados com alta sensibilidade, rápida resposta, tamanho pequeno e de razoável custo. Entretanto, o condicionador geralmente utilizado para processar os sinais do sensor SAW requer equipamentos eletrônicos grandes e de alto custo, como por exemplo analisadores de rede, analisadores de espectro, ou contadores de frequência. Neste trabalho, um novo condicionador é proposto para sensores SAW (do tipo linha de atraso). Este condicionador evita o uso de tais equipamentos, pois faz uma conversão direta da grandeza a ser medida para uma palavra digital. Uma malha de travamento de atraso totalmente digital é utilizada para medir variações no atraso do sinal passando através do sensor. Como estudo de caso, projetamos um protótipo em circuito integrado deste condicionador para um sensor SAW de umidade. O condicionador foi fabricado em tecnologia GF CMOS 130 nm, e ocupa uma área de 0.433 mm<sup>2</sup>. Exceto por dois comparadores, o condicionador é inteiramente composto por circuitos lógicos padrão. Este condicionador foi testado sozinho e dentro do setup proposto para medição de umidade. Quatro soluções salinas saturadas foram utilizadas para criar quatro ambientes com umidades relativas específicas na faixa de 32.8 a 90 %. O setup foi testado nestes quatro pontos de umidade, e os resultados mostram quatro níveis distintos na resposta do condicionador. Estes resultados foram replicados diversas vezes com razoavel reprodutibilidade. Baseando-se nestas medições, demonstramos a operação correta do novo condicionador de sinais para sensor SAW proposto neste trabalho.

**Palavras-chave**: Sensor SAW, malha de travamento de atraso, umidade relativa, CMOS.

### RESUMO EXPANDIDO

### Introdução

Sensores por onda acústica de superfície, ou simplesmente sensores SAW (do inglês *Surface Acoustic Wave*), tem sido demostrado fabricáveis em uma ampla variedade de aplicações, agindo como transdutores de grandezas físicas, químicas e biológicas para grandezas elétricas. Na literatura, estes sensores são amplamente reportados com alta responsividade, rápida resposta temporal, tamanho reduzido e razoável custo de fabricação. Porém, os condicionadores usualmente utilizados para processar os sinais destes sensores requerem equipamentos eletrônicos grandes e caros, como analisadores de rede, analisadores de espectro, e contadores de frequência. Este trabalho propõem uma nova forma de condicionar sensores SAW-DL (dispositivo SAW do tipo linha de atraso). Um sensor SAW-DL de umidade relativa é utilizado como estudo de caso. Um DLL (do inglês *Delay Locked Loop*) é utilizado para medir o atraso causado pelo sensor, que se torna sensível à umidade relativa após a deposição de um filme fino de óxido de grafeno.

### **Objetivos**

O objetivo geral deste trabalho é desenvolver um circuito integrado para realizar o condicionamento de um sensor SAW-DL de umidade relativa desenvolvido e fabricado pelo Dr. Sergey Balashov (CTI Renato Archer).

Os objetivos específicos deste trabalho são:

- Estudar o DLL como um sistema de medição de atrasos temporais, e como isso pode ser aplicado como um condicionador de sensores SAW-DL;

- Estudar a arquitetura proposta através de uma revisão bibliográfica e de modelos matemáticos;

- Projetar um circuito integrado, com especial atenção a testabilidade do circuito;

- Medir as funcionalidades do circuito integrado isolado;

- Projetar um setup confiável para realizar a medição de umidade relativa, contendo o sensor e o circuito integrado;

- Medir umidade relativa com este setup para verificar o comportamento esperado do condicionador proposto;

### Metodologia

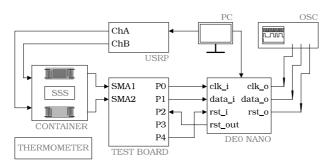

A metodologia para atingir os objetivos propostos começou com uma revisão bibliográfica do estado da arte em sensores SAW. A partir desta revisão bibliográfica foi possível entender melhor os princípios físicos da operação do sensor. Após esta etapa, passou-se para o estudo do DLL, utilizando artigos e análise de sistemas. Uma modelagem matemática foi obtida, o que possibilitou um entendimento muito mais profundo do funcionamento do DLL, e de como utilizá-lo para condicionar os sinais do sensor. Em sequência, foi passado para a fase de projeto do circuito integrado. Nesta etapa, a arquitetura foi projetada e simulada até que atingíssemos os requisitos e funcionalidades esperados. O projeto foi então mandado para a fabricação e encapsulamento. Quando ele voltou da fabricação, iniciamos as etapas de medição. Placas de circuito impresso foram desenvolvidas para alimentar, controlar e medir o circuito integrado. As funcionalidades isoladas do circuito foram medidas primeiramente. Após verificarmos que estas estavam de acordo com as expectativas teóricas e de simulação, partimos para o desenvolvimento de um setup completo de medição de umidade relativa. Este setup contém o condicionador de sinais, que é o circuito integrado projetado, uma placa USRP de rádio definido por software, e dois dispositivos SAW-DL, um que atua como o sensor e o outro como a referência. Utilizamos quatro soluções salinas saturadas para criar quatro ambientes com umidades relativas bem controladas e conhecidas. Estas soluções são amplamente utilizadas na calibração de sensores e medidores de umidade. Com este setup realizamos as medições destes quatro ambientes. O controle de temperatura do laboratório durante os testes foi controlado manualmente. e mantido em uma faixa de cerca de 2 ºC.

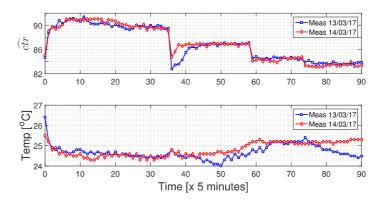

### Resultados e Discussão

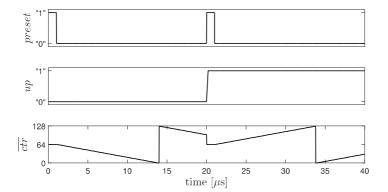

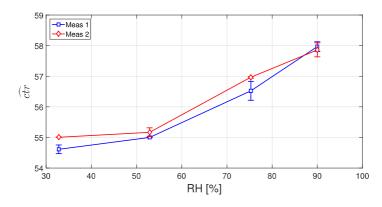

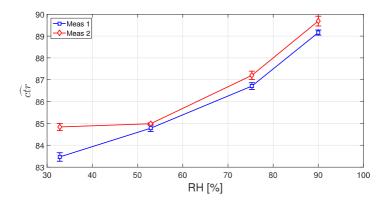

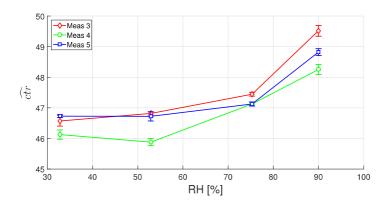

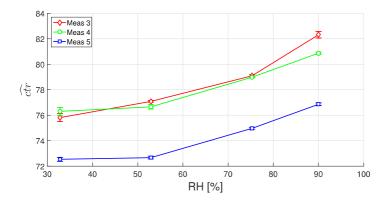

O setup de medição de umidade relativa proposto e projetado neste trabalho foi testado em quatro ambientes diferentes com umidade relativa controlada. Os dados obtidos com estas medições demonstram que o sistema responde à umidade relativa mais ou menos como as expectativas teóricas e por simulações. Foi possível medir umidade relativa numa faixa de 32.8 a 90.0 %. Quatro níveis distintos podem ser observados para as quatro condições de umidade. Os resultados foram bem reproduzidos entre dois dias consecutivos. É estimada uma variação de aproximadamente 6 no valor da palavra digital de saída do condicionador para a faixa de umidade relativa testada. Baseado na caracterização do DLL isolado, esta variação na palavra digital de saída se traduz a uma

variação de aproximadamente 15º na fase do sinal elétrico aplicado no sensor SAW-DL.

### Considerações finais

Foi possível atingir todos os objetivos propostos para este trabalho. O condicionador proposto foi estudado e posteriormente projetado e testado. Além dos testes isolados, o condicionador foi testado em um setup de medição de umidade relativa. Os resultados experimentais obtidos demonstram a correta operação do condicionador. Apesar de haverem diversas possíveis melhorias no circuito e no setup de medição, os dados obtidos validam a habilidade do sistema para descriminar níveis de umidade relativa.

**Palavras-chave:** Sensor SAW, malha de travamento de atraso, umidade relativa, CMOS.

# LIST OF FIGURES

| 1  | Upper view of the two most common SAW devices, the delay     |    |

|----|--------------------------------------------------------------|----|

|    | line (above) and the resonator (below)                       | 21 |

| 2  | Most common methods of conditioning SAW-DL sensors           | 24 |

| 3  | SAW-DL sensor conditioner with temperature compensation      | 25 |

| 4  | SAW-DL used in this work.                                    | 29 |

| 5  | Diagram of principles of the proposed conditioner            | 31 |

| 6  | The fully-digital DLL                                        | 33 |

| 7  | Phase detector response                                      | 35 |

| 8  | N <sup>th</sup> delay block structure                        | 37 |

| 9  | Discrete-time model for the fully-digital DLL                | 38 |

| 10 | Block diagram of the designed integrated circuit             | 41 |

| 11 | ESD protection structure for the IO pins                     | 45 |

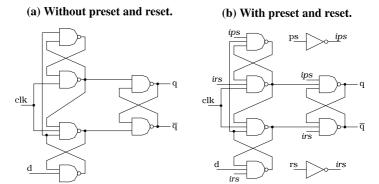

| 12 | D flip-flop topologies                                       | 47 |

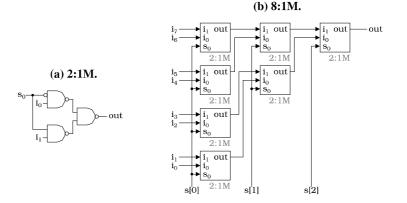

| 13 | Multiplexer topology                                         | 47 |

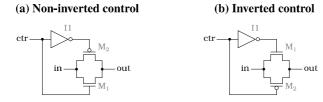

| 14 | Three-state switches topology                                | 48 |

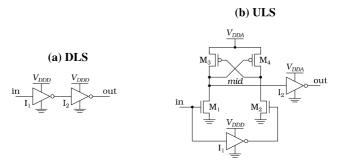

| 15 | Level shifters topologies                                    | 49 |

| 16 | Inverter chain buffers topology                              | 50 |

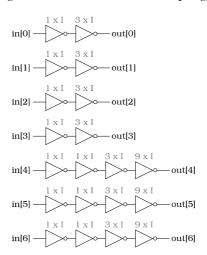

| 17 | Frequency divider                                            | 50 |

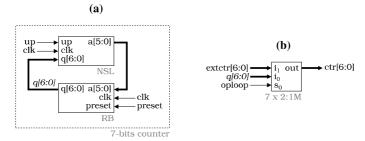

| 18 | 7-bits accumulator topology                                  | 52 |

| 19 | Next state logic of the 7-bits counter                       | 53 |

| 20 | Registers bank of the 7-bits counter                         | 53 |

| 21 | The implementation of the Toggle flip-flop used in the coun- |    |

|    | ter register bank                                            | 53 |

| 22 | Accumulator simulation result                                | 54 |

| 23 | Topology of one delay element                                | 56 |

| 24 | Post-layout simulation result of the DCDL transfer function  | 57 |

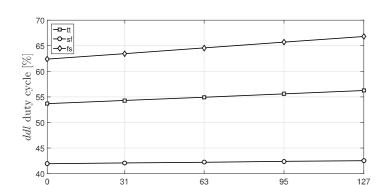

| 25 | Post-layout simulation of the DCDL output duty-cycle for ty- |    |

|    | pical and worse scenarios                                    | 58 |

| 26 | Input comparators topology                                   | 59 |

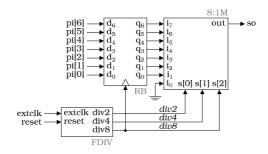

| 27 | Topology of the parallel-to-serial converter                 | 62 |

| 28 | P2S typical operation                                        | 62 |

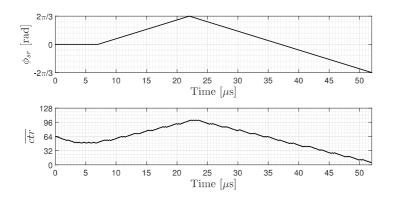

| 29 | Post-layout simulation of the whole DLL                      | 64 |

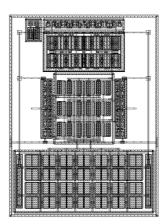

| 30 | Layout of the whole system                                   | 66 |

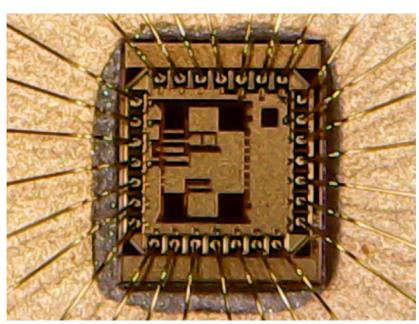

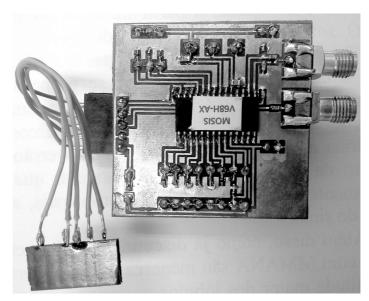

| 31 | Photography of the packaged IC                               | 67 |

| 32 | Test Board 1                                                 | 70 |

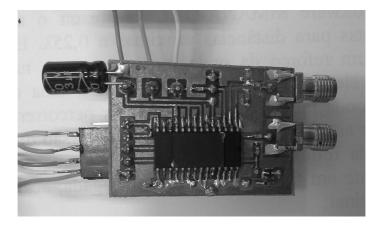

| 33 | Test Board 2                                                 | 70 |

| 34 | TB1 photography                                              | 71 |

| 35 | TB2 photography                                                           | 71  |

|----|---------------------------------------------------------------------------|-----|

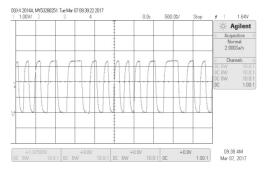

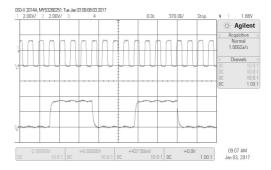

| 36 | Internal clock signal                                                     | 74  |

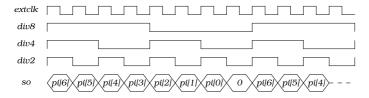

| 37 | External clock division                                                   | 75  |

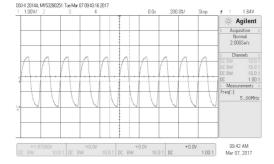

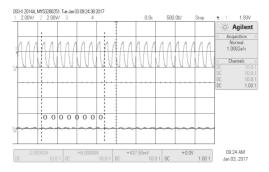

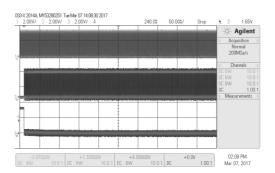

| 38 | Output data stream                                                        | 76  |

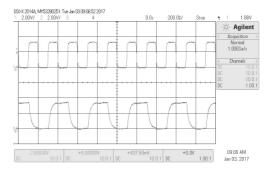

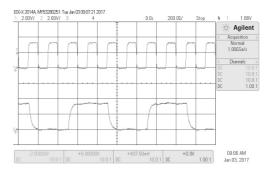

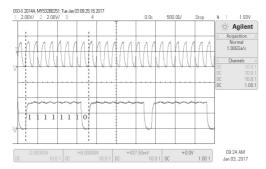

| 39 | Measurement of the delay caused by the DCDL                               | 79  |

| 40 | Measurement of the DCDL transfer function for $V_{DDD} = 1.2 \text{ V}$ . | 80  |

| 41 | Measurement of the DCDL transfer function for $V_{DDD} = 1.8 \text{ V}$ . | 80  |

| 42 | Test bench schematic for measuring the DLL response                       | 81  |

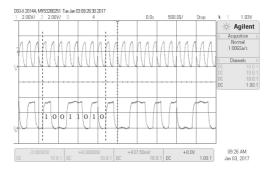

| 43 | Example of one data frame acquired in the oscilloscope                    | 81  |

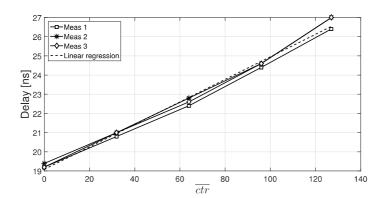

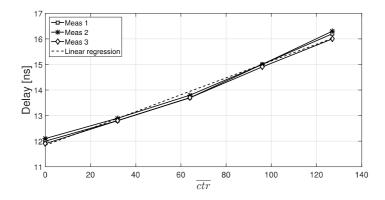

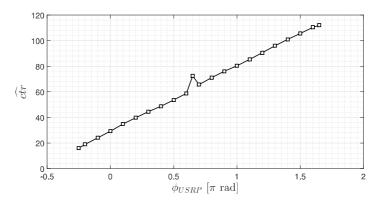

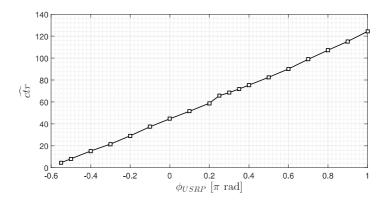

| 44 | TB1 DLL response                                                          | 82  |

| 45 | TB2 DLL response                                                          | 83  |

| 46 | One frame used to calculate 0.1 $\pi$ rad in Figure 44b                   | 85  |

| 47 | Test bench used to measure RH                                             | 88  |

| 48 | Picture of the test bench in the laboratory                               | 89  |

| 49 | Transient response of the measurement setup to the four refe-             |     |

|    | rence SSSs                                                                | 91  |

| 50 | Methodology to obtain the setup response to RH                            | 92  |

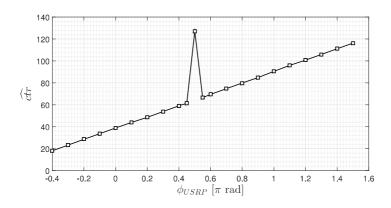

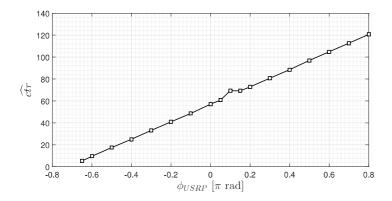

| 51 | TB1 response to RH                                                        | 93  |

| 52 | TB2 response to RH                                                        | 94  |

| 53 | Example of data frame acquired in the oscilloscope                        | 110 |

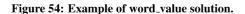

| 54 | Example of word_value solution                                            | 110 |

| 55 | USRP board output power                                                   | 112 |

| 56 | Layout of the combinational logic circuits                                | 119 |

| 57 | Layout of the D flip-flop with asynchronous preset and reset              | 120 |

| 58 | Layout of the 8:1 multiplexer                                             | 120 |

| 59 | Layout of the three-state swith with non-inverted control                 | 121 |

| 60 | Layout of the level shifters (not in the same scale)                      | 121 |

| 61 | Layout of the buffers (not in the same scale)                             | 121 |

| 62 | Layout of the frequency divider                                           | 122 |

| 63 | Layout of the 7-bits accumulator                                          | 122 |

| 64 | Layout of the delay element                                               | 122 |

| 65 | Layout of the DCDL                                                        | 123 |

| 66 | Layout of the input comparator                                            | 124 |

| 67 | Layout of the parallel-to-serial converter                                | 124 |

|    |                                                                           |     |

# LIST OF TABLES

| 1  | Selected research on SAW sensors                              | 27  |

|----|---------------------------------------------------------------|-----|

| 2  | Simulation results of one delay element                       | 56  |

| 3  | Post-layout simulation results of the DCDL                    | 57  |

| 4  | Transistors dimensions of the input comparators               | 60  |

| 5  | Output duty-cycle of the input comparator in corners          | 60  |

| 6  | Output duty-cycle of the input comparator in Monte Carlo      |     |

|    | (100 runs, process and mismatch)                              | 60  |

| 7  | Test multiplexer truth table                                  | 63  |

| 8  | Estimated power consumption                                   | 65  |

| 9  | Estimated DLL gain and $\delta$                               | 84  |

| 10 | Current consumption for $V_{DDD} = 1.2 \text{ V.} \dots$      | 85  |

| 11 | Current consumption for $V_{DDD} = 1.8 \text{ V.} \dots$      | 86  |

| 12 | $\widehat{ctr}$ vs RH for TB1 and $V_{DDD}$ = 1.2 V           | 92  |

| 13 | $\widehat{ctr}$ vs RH for TB1 and $V_{DDD}$ = 1.8 V           | 95  |

| 14 | $\widehat{ctr}$ vs RH for TB2 and $V_{DDD}$ = 1.2 V           | 95  |

| 15 | $\widehat{ctr}$ vs RH for TB2 and $V_{DDD}$ = 1.8 V           | 95  |

| 16 | Summary of the humidity test results for both test boards and |     |

|    | $V_{DDD}$ = 1.8 V                                             | 96  |

| 17 | Comparision with the selected research                        | 101 |

| 18 | 222                                                           | 113 |

| 19 | DLL curve for TB1 and $V_{DDD} = 1.8 \text{ V}$               | 114 |

| 20 | DLL curve for TB2 and $V_{DDD} = 1.2 \text{ V}$               | 115 |

| 21 | DLL curve for TB2 and $V_{DDD} = 1.8 \text{ V}$               |     |

| 22 | Temperatures during TB1 humidity tests                        |     |

| 23 | Temperatures during TB2 humidity tests                        | 117 |

### LIST OF ACRONYMS AND SYMBOLS

7BAC - 7-bits accumulator

CMOS - Complementary metal oxide semiconductor

CWA - Chemical warfare agent

DB - Diode bridge

DCDL - Digital-controlled delay line

DLL - Delay-locked loop

DLS - Down level shifter

ESD - Electrostatic discharge

FDIV - Frequency divider

GF - Global Foundries

IC - Integrated circuit

IC2 - Inverter chain buffer of 2 levels

ICBF - Inverter chain buffer

ICMP - Input comparator

IDT - Interdigital transducer

GO - Graphene Oxide

IO - Input/Output

LF - Loop filter

MIM - Metal-insulator-metal

MOS - Metal-oxide-semiconductor

MOSFET - MOS field effect transistor

MOSIS - Metal oxide semiconductor implementation service

NMOS - N-channel MOSFET

OB - Output buffer

P2S - Parallel-to-serial converter

PD - Phase detector

PMOS - P-channel MOSFET

PVA - Polyvinyl alcohol

RH - Relative humidity

SA - Spectrum analyzer

SAW - Surface acoustic wave

SAW-DL - SAW delay-line

SAW-R - SAW resonator

SSS - Saturated saline solution

TB1 - Test board 1

TB2 - Test board 2

TMUX - Test multiplexer

ULS - Up level shifter

VCO - Voltage-controlled oscillator

VCDL - Voltage-controlled delay line

VNA - Vector network analyzer

d - Period of the IDT

*K* - Frequency division ratio

$P_{clk}$  - Clock period (5 MHz)

$P_{ref}$  - Reference period (160 MHz)

*n* - Sample number

$\delta_l$  - Delay of the "low" delay path

$\delta_h$  - Delay of the "high" delay path

$\delta$  - Delay difference between  $\delta_h$  and  $\delta_l$

$au_{\Delta}$  - Total delay caused by the DCDL

$au_{\Delta_N}$  - Delay caused by the Nth delay block

$\phi$  - Phase difference between signals ddl and sch

$\tau_s$  - Delay between signals ref and sch

$\tau_d$  - Dealy between signals ref and ddl

$\tau_r$  - Delay caused by the reference channel

$\phi_i nitial$  - Initial phase between signals ddl and sch

$R_{DB}$  - Diode bridge resistor

$C_{si}$  - Internal supply capacitor

$\Delta_{t_r}$  - Time-delay between the rising edges of the input and output signals in a delay element

$\Delta_{t_f}$  - Time-delay between the falling edges of the input and output signals in a delay element

$\phi_{sr}$  - Phase between signals sch and rch

$R_P$  - Pull-down resistor

$R_C$  - Resistor used to smooth clock transitions

$C_S$  - Supply capacitor

$C_B$  - Bypass capacitor

# **CONTENT**

| 1 INTRODUCTION                               | 21 |

|----------------------------------------------|----|

| 1.1 SAW DEVICES                              | 21 |

| 1.2 THE SAW SENSOR                           | 23 |

| 1.3 SCOPE OF THIS PROJECT                    | 27 |

| 1.3.1 Case study - SAW-DL humidity sensor    | 28 |

| 1.4 NOTATION                                 | 29 |

| 2 PROPOSED CONDITIONER FOR SAW-DL SENSORS    | 31 |

| 2.1 DLL-BASED CONDITIONER FOR SAW-DL SENSORS | 31 |

| 2.2 THE FULLY-DIGITAL DLL                    | 33 |

| 2.2.1 Input Comparators                      | 34 |

| 2.2.2 Frequency divider                      | 34 |

| <b>2.2.3</b> Phase detector                  | 34 |

| 2.2.4 M-bit counter                          | 36 |

| 2.2.5 Digital-Controlled Delay Line          | 36 |

| 2.2.6 Fully-digital DLL analysis             | 37 |

| 3 CMOS CONDITIONER FOR A SAW-DL HUMIDITY     |    |

| SENSOR                                       | 41 |

| 3.1 SYSTEM TOPOLOGY AND TECHNOLOGY           | 42 |

| 3.2 ESD PROTECTION                           | 44 |

| 3.3 DIGITAL LIBRARY                          | 45 |

| 3.3.1 Combinational Logic                    | 46 |

| 3.3.2 D Flip-Flop                            | 46 |

| <b>3.3.3</b> Multiplexers                    | 47 |

| 3.3.4 Three-State Switches                   | 48 |

| 3.4 LEVEL SHIFTERS                           | 48 |

| 3.4.1 Topology                               | 48 |

| 3.5 INVERTER CHAIN BUFFERS                   | 49 |

| 3.5.1 Topology                               | 49 |

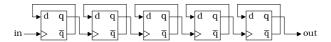

| 3.6 FREQUENCY DIVIDER                        | 50 |

| 3.6.1 Topology                               | 50 |

| 3.7 7-BITS ACCUMULATOR                       | 51 |

| 3.7.1 Topology                               | 51 |

| 3.7.2 Simulation results                     | 54 |

| 3.8 DIGITAL CONTROLLED DELAY LINE            | 54 |

| 3.8.1 Topology                               | 55 |

|                                              | 56 |

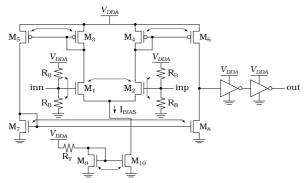

| 3.9 INPUT COMPARATORS                        | 58 |

| 3.9   | .1  | Topology                                    | 58  |

|-------|-----|---------------------------------------------|-----|

| 3.9   | .2  | Simulation results                          | 60  |

| 3.10  | PA  | RALLEL-TO-SERIAL CONVERTER                  | 61  |

| 3.1   | 0.1 | Topology                                    | 61  |

| 3.11  | TE  | ST MULTIPLEXER                              | 62  |

|       |     | STEM INTEGRATION                            | 63  |

| 3.1   | 2.1 | Layout                                      | 63  |

|       |     | Simulation Results                          | 64  |

|       |     | SUREMENTS OF THE DESIGNED CONDITIONER.      | 69  |

| 4.1   | TE  | ST BOARDS AND EQUIPMENTS                    | 69  |

| 4.1   | .1  | Test Boards                                 | 69  |

| 4.1   |     | Equipaments                                 | 72  |

| 4.2   | FU  | UNCTIONAL TESTS                             | 72  |

| 4.2   | .1  | Internal clock                              | 73  |

| 4.2   | .2  | External clock division                     | 73  |

| 4.2   | .3  | Output data stream                          | 74  |

| 4.2   | .4  | DCDL                                        | 77  |

| 4.2   | .5  | DLL                                         | 78  |

| 4.2   | .6  | Current consumption                         | 85  |

| 4.3   | Н   | JMIDITY TESTS                               | 87  |

| 4.3   | .1  | Humidity control                            | 87  |

| 4.3   | .2  | Temperature Control                         | 87  |

| 4.3   | .3  | Test Bench                                  | 88  |

| 4.3   | .4  | Transient Test                              | 90  |

| 4.3   | .5  | System response to RH                       | 91  |

| 4.3   | • • | Conclusions of the humidity tests           | 96  |

| 5 CC  |     | CLUSIONS                                    | 99  |

| 5.1   |     | COMMENDED IMPROVEMENTS FOR FUTURE DESIGN    | 101 |

| 5.2   | TC  | PICS FOR FUTURE WORKS                       | 102 |

| Refer | en  | ces                                         | 105 |

|       |     | ix A – Codes and Scripts                    | 107 |

| A.1   | DE  | E0-NANO VERILOG CODE                        | 107 |

| A.2   | W   | ORD VALUES                                  | 108 |

|       |     | ix B – Additional Test Results              | 111 |

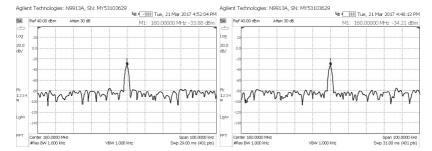

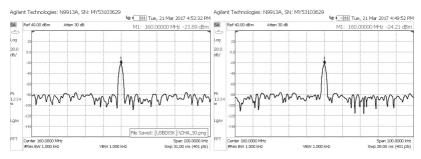

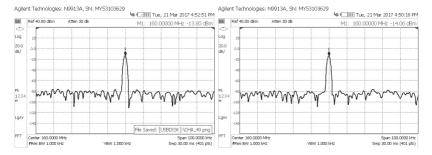

| B.1   | US  | SRP OUTPUT POWER                            | 111 |

| B.2   |     | L CURVES AVERAGES AND STANDARD DEVIATIONS . |     |

| B.3   |     | EMPERATURE DURING HUMIDITY TESTS            |     |

| Appe  | nd  | ix C – Layouts                              | 119 |

#### 1 INTRODUCTION

Surface Acoustic Wave (SAW) sensors have been demonstrated feasible in a wide variety of applications, acting as transducers of physical, chemical, and biological quantities to electrical quantities. However, the conditioner circuitries generally employed require expensive and large measurement equipments, such as vector network analyzers (VNA), spectrum analyzers (SA), or frequency counters. In this work we propose a novel conditioner for SAW-DL sensors that circumvents the use of these equipments. We also present the design and test of an integrated circuit prototype of this conditioner.

#### 1.1 SAW DEVICES

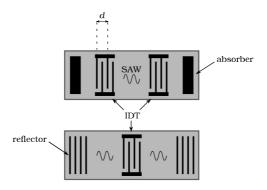

Surface Acoustic Wave (SAW) devices are electromechanical structures composed of a piezoelectric substrate and at least one electromechanical transducer. Figure 1 shows the two most common forms of these structures, the SAW Delay Line (SAW-DL), and the SAW Resonator (SAW-R). These devices are used in various applications, for instance in the generation of reference signals because of their high frequency stability. They are also often employed in the filtering of signals thanks to their narrow band-pass transfer function. Finally, since the 70s these devices have been used as sensors in a very broad range of applications, such as the sensing of chemical vapors (WOHLTJEN, 1984), temperature (MAINES *et al.*, 1969), humidity (CALIENDO *et al.*, 1997), and more recently the detection of cancer cells and other

Figure 1: Upper view of the two most common SAW devices, the delay line (above) and the resonator (below).

1 INTRODUCTION

biological structures (CAI et al., 2015).

A piezoelectric solid is a type of material capable of converting an electric field into a mechanical stress (CADY, 1947). Its particular atomic structure creates an electric field in the region where it is mechanically deformed. The inverse effect is also observed: when we apply an electric field the solid deforms. Piezoelectric materials are employed as the SAW devices substrates because of this conversion property aforementioned. Some examples of piezoelectric materials are the quartz, lithium niobate, potassium sodium tartrate (Rochelle salt), barium titanate, etc.

The transduction from an electric signal to a SAW happens by means of the interdigital transducers (IDT) (WHITE; VOLTMER, 1965). These electrodes are formed by the deposition of a thin-layer of metal over the piezoelectric substrate of the SAW device. When a voltage is applied across the terminals of the IDT, an electric field emerges between the fingers. As a consequence, a mechanical deformation occurs at the surface of the substrate, due to its piezoelectric property. If the applied voltage is a periodic signal, a mechanical wave is generated on the surface of the solid. The maximum conversion of energy, from electrical to mechanical, occurs when the wavelength of the SAW equals the period *d* of the IDT (JR. *et al.*, 1997).

The mechanical wave that is generated in the solid by the process described above is known as a Rayleigh wave, in honor of Lord Rayleigh, pioneer physicist in the studies of waves in solid surfaces (RAYLEIGH, 1885). The particles that compose the surface layers of the solid have two components of displacement, a longitudinal component, i.e., in the direction of the propagating wave, and a component in the direction of the vector normal to the surface (WOHLTJEN, 1984). These two components vibrate, which results in the propagation of a mechanical wave, without the transport of matter. The great majority of the energy associated with this perturbation is within one wavelength depth, and that is why they are called surface waves. This particular characteristic is responsible for the usually high sensitivity of the SAW sensors.

The most common SAW device structures are the delay line (SAW-DL) and the resonator (SAW-R), shown in Figure 1. The SAW-DL is composed of two IDTs and energy absorbers. One of the transducers is used as the transmitter and the other as the receiver of the SAW propagating through the substrate. The absorbers attenuate undesired reflections from the boundaries of the device, thereby ensuring that the flow of energy happens mostly from one transducer to the other. One interesting characteristic is that the delay caused by the SAW-DL is about 10<sup>5</sup> times larger than that caused by an elec-

1.2 The SAW sensor 23

tric transmission line with the same length (the speed of the Rayleigh wave in a quartz crystal is approximately 3100 m/s, about  $10^{-5}$  times the speed of light in vacuum). This can be used to fabricate much shorter delay lines.

The SAW-R is composed of one IDT and energy reflectors. The transducer serves as both transmitter and receiver of the SAW. The wave that is generated by the IDT propagates through the substrate in both directions, and is reflected back to the IDT with a different amplitude and phase. This difference can be detected by measuring the impedance or reflection coefficient seeing across the IDT terminals. In the resonance frequency, the device presents a complex impedance which is a function of the SAW speed, and the distance between the IDT and the reflectors. These devices are usually employed in oscillator, due to their high frequency stability.

### 1.2 THE SAW SENSOR

SAW devices can be used as transducers of physical, chemical, and biological quantities to an electric signal. The measurand interacts with the surface on which the SAW is traveling, and this interaction causes a variation in the phase-velocity and amplitude of the propagating wave. This variation can be detected as a shift in the amplitude or delay of the electric signal applied to the sensor. For instances, one can take advantage of the temperature-delay coefficient of a SAW in an specific substrate in order to create a temperature sensor. A form of using SAW devices to sense chemical or biological quantities is to coat the delay-path (surface region through where the SAW propagates) with a material that absorbs or creates bond with the measurand. For instance, the relative humidity sensor used in this work is coated with a thin-layer of graphene oxide (GO), which can absorb water molecules. This causes a mass-loading effect in the surface, which decreases the SAW phasevelocity and increases the propagation delay. In this section we review the most common methods of conditioning SAW sensors, and present some interesting applications and researches.

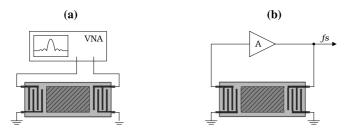

The most traditional methods of conditioning and measuring a SAW sensor response are presented in Figures 2a and 2b. One can directly measure the frequency response of the device in a VNA and estimate the group delay through the transmission coefficient of the SAW-DL. In the case of a SAW-R, the VNA measures variations in the reflection coefficient as a function of the measurand. This method can offer a high measurement precision, however it requires an expensive and large electronic equipment. Another

Figure 2: Most common methods of conditioning SAW-DL sensors.

method, which is depicted in Figure 2b, consists of using the SAW device as the element that determines the frequency of an oscillator (MAINES *et al.*, 1969) (WOHLTJEN, 1984). In order for the circuit to oscillate, the Barkhausen criteria must be fulfilled. Therefore, the amplifier A must be able to add enough power to compensate for the insertion loss of the SAW-DL, and the total phase in the loop must be a multiple of  $2\pi$ . The measurand interacts with the surface and changes the delay of the SAW, which reflects in small variations around the central oscillation frequency, determined by the IDT structure. Therefore, the quantity of the measurand is translated to a variation in the frequency fs. Similarly, an oscillator can be made with a SAW-R. Finally, fs is measured with a frequency counter, or with a SA. This is by far the most common conditioner for SAW sensors, because it generally offers a high measurement precision. However, it also depends on usually expensive electronic equipments.

An interesting variation of the conditioner presented in Figure 2b was proposed in (REEDER  $et\ al.$ , 1975) for compensating temperature in pressure measurements. An adaptation of this architecture is depicted in Figure 3. Two SAW-DL are fabricated over the same substrate. One of them is coated with a thin-film of a sensitive material (sensing channel), and the other is left uncoated (reference channel). The frequency difference fd between the reference and sense signals is obtained by mixing and low-pass filtering fr and fs. This new signal contains in its frequency the quantity of the measurand. Since both delay-paths are subjected to the same temperature, because they are in the same substrate and close to each other, both frequencies fr and fs vary the same amount as a function of this environment parameter. Therefore, temperature variations do not considerably change the frequency fd, i.e., this architecture compensates temperature. It can also compensate for aging, since both SAW-DL are subjected to the same environment over time. Although the output signal has a much lower frequency than fs, this

1.2 The SAW sensor 25

Figure 3: SAW-DL sensor conditioner with temperature compensation.

conditioner still requires a form of measuring frequency.

Temperature was the first parameter to be measured with a SAW device (MAINES *et al.*, 1969). The initial intention of the authors was to determine the relation between temperature and delay in order to compensate this undesired behavior in other applications of SAW devices (e.g., transversal filter and dispersive delay line). This research led to a whole new field of study where SAW devices are employed as sensor in a great variety of applications. In temperature SAW sensors, the expansion (or contraction) of the delay-path and changes in the velocity of the mechanical wave due to temperature are used as the transduction mechanism. For instance, the authors in (BORRERO *et al.*, 2013) used a 128° YX cut of LiNbO<sub>3</sub> (lithium niobate) to fabricate a SAW-R temperature sensor. The reflection coefficient was measured in a VNA in order to detect the frequency variation in the resonance as a function of the temperature variation. The result was a linear relationship (-5.83 kHz/°C) between the resonance frequency and the temperature.

In chemical and biological SAW sensors a sensitive thin-layer is chosen in order to absorb or to form chemical bonds with a specific analyte or organism. This trapping causes a mass-loading in the surface of the device, which is responsible for the shift in the propagation velocity of the SAW. In (RAJ et al., 2013) four one-port SAW-R devices were covered with four different oxide thin-layers (ZnO, TeO<sub>2</sub>, SnO<sub>2</sub>, and TiO<sub>2</sub>). They were used to compose an E-nose (electronic nose) array to detect chemical warfare agents (CWA), which are vapors very dangerous to humans, even in low concentration. In order to condition the sensors signals, the authors use a circuitry similar to the one presented in Figure 3, where one uncoated device is used

1 INTRODUCTION

in a reference oscillator, and the other four coated devices are used in four sense oscillators (RAPP *et al.*, 2000). The information is in the frequency difference between the reference and the sense oscillators. In this case a multiplexing technique has to be used in order to allow only one sense oscillator to operate each time. The E-nose array could rightfully classify four CWA simulants (DMMP, DBS, CEPS, and DECP), even in the presence of some interferent vapors (petrol, diesel, kerosene, VOCs, and water).

A great variety of organic and inorganic chemical vapors can be detected by SAW sensors. A few examples are: toluene, octane, methanol, ethanol, alcohol, esters, carboxylic acids, NH<sub>3</sub>, CO, CH<sub>4</sub>, H<sub>2</sub>, O<sub>2</sub>, etc. Two vast reviews on SAW vapor sensors are presented in (AFZAL *et al.*, 2013) and (BO *et al.*, 2016).

SAW sensors have also a promising future in biological analysis. In (CAI *et al.*, 2015) a SAW-R operating at 6.4 GHz (third-order harmonic) is used to detect specific mouse cancer cells and DNA bases. The SAW-R is analyzed in a VNA in order to detect frequency shifts in the reflection coefficient as a response to variations in the concentration of these substances. An ultra-high sensitivity was obtained, which makes the sensor able to detect a single hybridized DNA base, and sense two mouse living cancer cells: mammary adenocarcinoma (EMT6) and fibroblast (3T3) cells.

Finally, SAW sensors have been employed in the measurement of humidity levels with relatively high responsivity and small response time (RITTERSMA, 2002), as compared to other humidity sensors (e.g., capacitive and resistive). In (PENZA; CASSANO, 2000) a commercial SAW-DL operating at 433.92 MHz is coated with a PVA (polyvinyl-alcohol) film, a hygroscopic polymer which absorbs water molecules. The absorption causes a massloading in the surface of the device, which decreases the propagation velocity of the SAW. The conditioner used in this work is similar to the one presented in Figure 3. In (CALIENDO *et al.*, 1997) the authors investigate the response of several chemical interactive material membranes to relative humidity (RH) on the exposure to water, ethanol, and acetone vapors. They report a considerable variation in the phase velocity and in the acoustic attenuation of the signals propagating along the surface of the SAW-DL as a function of the gas concentration.

In the literature, SAW sensors are widely reported with high sensitivity, fast response time, small size, and reasonable cost (AFZAL *et al.*, 2013), (BO *et al.*, 2016), (LEE; LEE, 2005), (RAPP *et al.*, 2000). The researches presented in this section also demonstrate the wide variety of applications for these sensors, ranging from the transduction of temperature and humi-

|             | (PENZA;        | (BORRERO et    | (RAJ et al.,  | (CAI et al.,             |

|-------------|----------------|----------------|---------------|--------------------------|

|             | CASSANO,       | al., 2013)     | 2013)         | 2015)                    |

|             | 2000)          |                |               |                          |

| Type of SAW | Delay Line     | Resonator      | Resonator     | Resonator                |

| sensor      |                |                |               |                          |

| Operating   | 468 MHz        | 65 MHz         | 433.9 MHz     | 6.4 GHz (3 <sup>rd</sup> |

| Frequency   |                |                |               | harm)                    |

| Measurand   | Relative Humi- | Pressure,      | Chemical War- | Mouse cancer             |

|             | dity           | Temperature,   | fare Agents   | cells and DNA            |

|             |                | Impedance      | _             | bases                    |

| Output For- | Frequency      | Reflection Co- | Frequency     | Reflection Co-           |

| mat         |                | efficient      |               | efficient                |

| Required    | Frequency      | VNA            | SA            | VNA                      |

| Equipments  | Counter + PC   |                |               |                          |

Table 1: Selected research on SAW sensors.

dity, to the detection of chemical warfare agents and cancer cells. Therefore, the SAW technology has a promising future in sensor applications. Table 1 summarizes the selected researches on SAW sensors presented in this section.

However, the circuitry generally employed in the conditioning of these sensors does not offer a complete solution, as can be notice by the equipments usually required to condition these sensors. As stated in (LEE; LEE, 2005) "In general, gravimetric humidity sensors¹ provide a high sensitivity, a rapid response time and a simple experimental setup. However, they generally require expensive driving and detection electronics". In (BO *et al.*, 2016) it is stated that "Though quite a lot of advantages have been shown for SAW sensors, various challenges still exist. The biggest one is the peripheral circuit. Frequency response and time delay is measured using a network analyzer, which is large and expensive".

#### 1.3 SCOPE OF THIS PROJECT

The references presented in the last section show how vast is the field of SAW sensors. A multitude of physical, chemical, and biological quantities can be translated to variations in amplitude, phase, and/or frequency of an electric signal through these transducers. However, the conditioning of these sensors still relies on large and expensive laboratory equipments (SA, VNA, frequency counter). The main focus of researches is on new sensitive thin-layers to detect different analytes, always relying on the traditional conditioning techniques. Therefore, it is clear that the electronic circuitry which is used to condition the SAW sensors can still be improved. This research

<sup>&</sup>lt;sup>1</sup>SAW sensors are classified as gravimetric sensors.

focus on the conditioner circuitry for SAW-DL sensors.

The general objective of this work was to design an integrated circuit conditioner for a SAW-DL humidity sensor fabricated by Dr. Sergey Balashov (CTI Renato Archer). The novel conditioner proposed in this dissertation has the main advantage of direct converting the measurand to a digital word, which can be acquired and processed by a microcontroller or computer. Although the focus was to develop a conditioner for the humidity sensor, we understand that the proposed architecture can be extended to any SAW-DL sensor which can translate a measurand of interest to a time-delay of a signal.

The specific objectives of this work were:

- To study the DLL as a time-delay measurement system, and how it can be applied as the conditioner for SAW-DL sensors;

- To study the proposed architecture through literature review and mathematical models;

- To design an integrated circuit, with special attention to the testability of this circuit:

- To measure the IC stand-alone functionalities;

- To design a reliable setup to measure humidity, containing the sensor and the IC;

- To measure humidity with this setup in order to verify the expected behavior of the proposed conditioner.

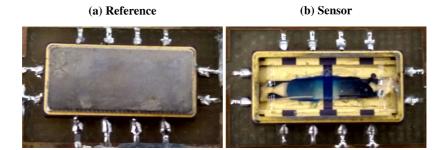

# 1.3.1 Case study - SAW-DL humidity sensor

The SAW-DLs used in this work are depicted in Figures 4a (used as the reference channel) and 4b (used as the sensing channel). They were fabricated on a ST-cut Quartz substrate and coated with a sub-micron-thick film of graphene oxide (GO), which is hygroscopic. The details of the fabrication process of these devices are published elsewhere (BALASHOV *et al.*, 2012). The devices were not especifically designed for this system. These SAW sensors were already fabricated, and we designed the integrated circuit to condition them. Their operating frequency is 160 MHz.

1.4 Notation 29

Figure 4: SAW-DL used in this work.

### 1.4 NOTATION

The following notation is adopted throughout this document:

- Signals are labeled in lower, italic case. E.g. up.

- The inputs and outputs of internal blocks are labeled in lower, bold case. E.g. **up**. Notice that *up* is referring to a signal, and **up** to an IO.

- The inputs and outputs of the integrated circuit and test board pins are labeled in upper, bold case. E.g. **EXTCLK**.

- A signal array is denoted as *a*[3:0], from MSB to LSB. Similarly, an internal IO array is denoted as **a**[3:0], and an IC IO array as **A**[3:0].

- In some parts of the analysis, the decimal value of a digital word is required. This is denoted by  $\overline{a}$ , and should be read as the value of the word a/3:0/3.

- Blocks, subsystems, and circuit elements are labeled in simple upper case.

30

### 2 PROPOSED CONDITIONER FOR SAW-DL SENSORS

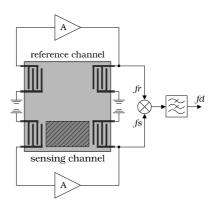

In this chapter we present the proposed signal conditioner for generic SAW-DL sensors (ROTTAVA *et al.*, 2016). The proposed architecture is depicted in Figure 5. It is composed of two SAW-DL devices, one acting as the sensing channel, and one as the reference channel, and a Delay-Locked Loop (DLL). In this architecture the SAW-DL sensor is in open-loop configuration, differing from the most common approach where it is in the feedback loop of an oscillator (see Figure 2b). Therefore, the information about the environmental parameter under measure in conveyed in the delay of a signal, rather than in its frequency. The DLL performs the function of tracking this delay, and by doing so the control signal *ctr* (filtered-error signal) allows a direct measure of the delay.

The chapter starts with a detailed explanation of the novel architecture. Then, we present the fully-digital DLL and analyze it as a discrete-time system. This analysis gives us some important insights about the system behavior.

### 2.1 DLL-BASED CONDITIONER FOR SAW-DL SENSORS

The proposed conditioner is depicted in Figure 5. A reference signal *ref* is applied to two SAW-DLs, one of them sensitive to an environmental parameter of interest (relative humidity in our case), and the other non-sensitive. The former acts as the sensing channel (whose output is *sch*), and the later as the reference channel (*rch*). Since both devices are in an open-loop configuration, the information we want to measure is conveyed in the time-delay between the signals *sch* and *rch*. This is the fundamental difference between

ref rch VCDL ddl PD LF ctr

sch Delay-Locked Loop

Figure 5: Diagram of principles of the proposed conditioner.

our measurement setup and the classical one presented in Figure 2b. This time-delay is then measured with a Delay-Locked Loop.

The DLL was first proposed as a form of measuring the time-delay between two correlated signals for radar applications (SPILKER; MAGILL, 1961)<sup>1</sup>. A typical DLL, as the one in Figure 5, is composed of a voltage-controlled delay line (VCDL), a phase detector (PD), and a loop filter (LF). The VCDL is a system that adds delay to the signal *ddl* (in relation to *rch*) in proportion to the voltage level of *ctr*. The PD generates a response proportional to the phase difference between its input signals. The LF is a first-order integrator which accumulates the phase difference throughout the operation in order to generate the control signal *ctr*.

The DLL is a negative-feedback system which controls the VCDL in order to phase-align *ddl* and *sch*. These signals are compared in the PD and the result is integrated in the LF. The filtered-error signal *ctr* is fed back to the VCDL and controls the increment or decrement of the delay between *ddl* and *rch*, in order to phase-align *ddl* to *sch*. Once the system reaches equilibrium, the time-delay between the signals in the input of the PD is kept constant throughout operation, as long as perturbations are not too strong, and the blocks do not saturate.

Perturbations in the time-delay of the input signals *sch* and *rch* are compensated by the system in the direction of phase-aligning *ddl* and *sch*. For instance, if the environmental parameter to be measured acts in the sensing channel by increasing the delay of *sch* in relation to *rch*, the delay caused by the VCDL also has to increase in the same amount in order to maintain the system locked in delay. Once the DLL reaches the new equilibrium, the value of the filtered-error signal *ctr* is increased in proportion to the increment in the delay of the sensing channel. Therefore, the proposed architecture directly converts variations in the environmental parameter being measured by the SAW-DL into a voltage level.

The reference channel serves to compensate for temperature (BA-LASHOV *et al.*, 2014). If the two devices are fabricated over the same substrate, the temperature will equally affect both delay paths, which will make the delays in signals *rch* and *sch* increase in the same proportion. The result is a desensitization of the system response to temperature. However, in this work we only had access to separate SAW devices for the reference and sensing channels. Therefore, the compensation is not guaranteed, since the

<sup>&</sup>lt;sup>1</sup>The system is called Delay-Lock Discriminator. The DLL is a more generic system which can be use to measure time-delays (in the case of this publication), but also in data and clock recovery, and a great variety of other applications.

devices are in different substrates and are distant from each other.

The next section presents the fully-digital implementation of the DLL which was used in this work. Each block of the system is described in detail, and a simplified model for the DLL is developed to demonstrate its principle of operation. For a more detailed analysis of the DLL operation, the reader is referred to (KIM *et al.*, 2003).

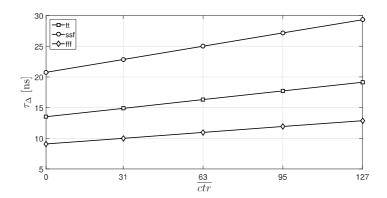

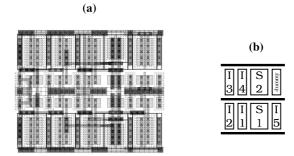

### 2.2 THE FULLY-DIGITAL DLL

Voltage-controlled delay lines are frequently designed with a MOS transistor as a voltage controlled resistor in a RC filter, or with a current starving structure as the element to control the delay (BAE *et al.*, 2005) (KUO; MA, 2013). This results in a non-linear transfer function for this block. Since the behaviour of the SAW-DL sensor was not known previously to the design (its delay vs RH response), we decided to investigate a VCDL with a linear (or at least nearly linear) response. This led us to the idea of creating small delay elements with only two possible states: a "high" delay path and a "low" delay path. These delay elements are concatenated to create what we call a Digital-Controlled Delay Line (DCDL), which is controlled by a digital word, instead of a voltage level. Since our control element is digital, we decided to adopt a fully-digital architecture for the rest of the DLL (MESGARZADEH; ALVANDPOUR, 2009). A fully-digital structure also has the advantages of low-area consumption.

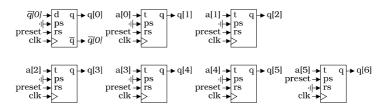

The block diagram for the fully-digital DLL is presented in Figure 6. It is composed of two input comparators, a D flip-flop employed as the PD, a frequency divider (FDIV), an M-bit counter, and the DCDL. The incoming

Figure 6: The fully-digital DLL.

signals from the SAW devices are digitized in the comparators to obtain *rch* and *sch*. Apart from these two blocks, all the remaining blocks can be fully-implemented with standard logic circuits. The rest of this chapter is dedicated to a discussion and analysis of each individual block, followed by a mathematical modeling of the whole system.

# 2.2.1 Input Comparators

The function of the input comparators is to saturate the incoming signals from the SAW devices to high and low logic levels. The only important information we want from these signals is their transitions (rising and falling edges), which convey their phase. Therefore, the function of the input comparators is to convert the low-amplitude sinusoidal signals into rail-to-rail square signals.

## 2.2.2 Frequency divider

The state of the system is updated every rising edge of *clk*. This signal is generated by dividing the frequency of *sch* (which is the same of *ref* frequency) by *K*. Therefore, the *clk* period is given by:

$$P_{clk} = KP_{ref}, (1)$$

where  $P_{ref}$  is the period of the reference signal. From now on, in order to model the DLL we will use the variable n to represent the sample number, i.e., one clk period.

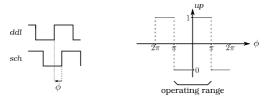

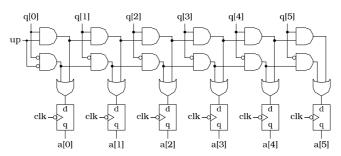

### 2.2.3 Phase detector

The phase detection is performed by a D flip-flop. If the rising edge of the signal *ddl*, which is being applied to the clock input of the flip-flop, occurs before the rising edge of *sch*, applied to the D input, it means that the former is phase-advance in relation to the latter. As a result, signal *up* receives logic level '1'. The other possibility is that *ddl* is phase-delayed in relation to *sch*. In this case, *up* goes to logic level '0'.

The phase difference between signals ddl and sch as a function of the

delays from ref to ddl  $(\tau_d)$  and from ref to sch  $(\tau_s)$  is given by:

$$\phi[n] = \frac{2\pi}{P_{ref}} \left( \tau_s[n] - \tau_d[n] \right), \tag{2}$$

where the term  $2\pi/P_{ref}$  converts a time-delay into a phase-delay. This PD can only detect the wrapped phase difference in the range  $(-\pi,\pi)$  between the two signals, as illustrated in Figure 7. Therefore, the result of Equation 2 must be wrapped to the interval  $(-\pi,\pi)$ .

Figure 7: Phase detector response.

Once the system reaches an equilibrium, the phase difference  $\phi[n]$  must never surpass  $\pm \pi$ , otherwise the system will reach another equilibrium (one reference period before, or one after). In other words, the system must be fast enough in order to compensate any possible perturbation in the delay of the signal sch caused by variations in the measurand.

The result generated by the PD as a function of the wrapped phase difference is then:

$$up[n] = \begin{cases} \text{`0'}, & \text{if } -\pi < \phi[n] < 0 \\ \text{`1'}, & \text{if } 0 < \phi[n] < \pi \end{cases}$$

(3)

This PD generates only two possible outcomes: signal ddl is either phase-advanced in relation to sch, which makes up = '1', or it is phase-delayed, which makes up = '0'. Therefore, the borders of the two signals will never be perfectly aligned. Even when the system reaches equilibrium, and there are no external perturbations, there will always be an oscillation between at least two states of the accumulator. This can be treated as quantization noise which is observed in analog-to-digital conversion.

#### 2.2.4 M-bit counter

The M-bit counter serves as a first-order integrator, or an accumulator. Its rate of update is determined by the signal clk. At each rising edge of this signal, the counter accumulates a unit depending on the value of the flag up. If up[n-1] = 0, the value of the digital word ctr[M-1:0], namely  $\overline{ctr}$ , is decreased by 1, else  $\overline{ctr}$  is increased by 1. We can model the behavior of the counter at sample n as:

$$\overline{ctr}[n] = \begin{cases} \overline{ctr}[n-1] - 1, & \text{if } up[n-1] = \text{`0'} \\ \overline{ctr}[n-1] + 1, & \text{if } up[n-1] = \text{`1'} \end{cases}$$

(4)

or in terms of the wrapped phase  $\phi$ :

$$\overline{ctr}[n] = \begin{cases}

\overline{ctr}[n-1] - 1, & \text{if } -\pi < \phi[n-1] < 0 \\

\overline{ctr}[n-1] + 1, & \text{if } 0 < \phi[n-1] < \pi

\end{cases}$$

(5)

Notice that ctr[N] means the N<sup>th</sup> bit of the digital word, and  $\overline{ctr}[n]$  means the decimal value of the digital word at sample n, which is given by:

$$\overline{ctr} = 2^{0}ctr[0] + 2^{1}ctr[1] + \dots + 2^{M-1}ctr[M-1].$$

(6)

The counter can be asynchronously set to a predefined value when *reset* signal is high, which allows us to force an initial state in the system. This value is chosen  $2^{M}/2$ , half the maximum value of  $\overline{ctr}$ , in order to allow the system to swing in both directions, increasing or decreasing the delay of the DCDL.

The value of  $\overline{ctr}$  is limited to the interval  $[0,2^M-1]$ . When these limits are reached, the controller no longer follows the behavior of Equation 4. These limits must be avoided by the designer.

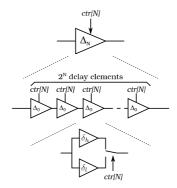

# 2.2.5 Digital-Controlled Delay Line

The DCDL is composed of M delay blocks,  $\Delta_0$  to  $\Delta_{M-1}$ . Each delay block is composed of a number of cascaded delay elements, which increases by a power of two at each level. Therefore, the N<sup>th</sup> delay block has 2<sup>N</sup> delay elements, as depicted in Figure 8. A delay element can be realized by a few inverters and a few switches to choose between a "high" delay-path ( $\delta_h$  seconds of delay) and a "low" delay-path ( $\delta_l$  seconds of delay). This implemen-

tation circumvents the use of non-linear devices for controlling the delay of the VCDL, avoiding undesired non-linear effects. This is important because the conversion gain of the DLL is directly related to the transfer function of the DCDL.

Figure 8: N<sup>th</sup> delay block structure.

The time-delay caused by the N<sup>th</sup> delay block is given by:

$$\tau_{\Lambda_N} = 2^N \left[ \delta ctr[N] + \delta_l \right],\tag{7}$$

where  $\delta = \delta_h$  -  $\delta_l$  is called the delay step or gain of the DCDL. The total time-delay caused by the DCDL is the summation of the time-delays of each delay block:

$$\tau_{\Delta} = \tau_{\Delta_0} + \tau_{\Delta_1} + \dots + \tau_{\Delta_{M-1}}, \tag{8}$$

which can be written in terms of  $\overline{ctr}[n]$  as:

$$\tau_{\Delta}[n] = \delta \ \overline{ctr}[n] + (2^M - 1)\delta_l. \tag{9}$$

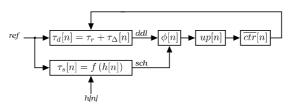

# 2.2.6 Fully-digital DLL analysis

A model for the fully-digital DLL as a discrete-time system is presented in Figure 9. The mathematical models for each block were obtained based on the behavior we expect for each one. Now we develop a mathematical analysis of this system, which gives us some important insights about its operation.

The time-delay between *ref* and *ddl* at sample *n* is the sum of the delay caused by the reference SAW-DL  $\tau_r$  and the delay caused by the DCDL  $\tau_{\Delta}[n]$ :

Figure 9: Discrete-time model for the fully-digital DLL.

$$\tau_d[n] = \tau_{\Delta}[n] + \tau_r

= \delta \overline{ctr}[n] + (2^M - 1)\delta_l + \tau_r.$$

(10)

The time-delay between ref and sch at sample n equals the delay caused by the sensing SAW-DL, which is related to the measurand value h[n]:

$$\tau_s[n] = f(h[n]), \tag{11}$$

where f() is the function that relates the measurand to the delay caused by the sensing device.

Equation 2 can be written in terms of an initial wrapped-phase  $\phi[0]$  and variations in the delays  $\tau_s$  and  $\tau_d$  with respect to an arbitrary initial sample (n = 0) as:

$$\phi[n] = \phi[0] + \frac{2\pi}{P_{ref}} \left[ (\tau_s[n] - \tau_s[0]) - (\tau_d[n] - \tau_d[0]) \right]. \tag{12}$$

By replacing Equations 10 and 11 into Equation 12 we get:

$$\phi[n] = \phi[0] + \frac{2\pi}{P_{ref}} \{ [f(h[n]) - f(h[0])] - [\delta \, \overline{ctr}[n] - \delta \, \overline{ctr}[0]] \}.$$

(13)

Let us first analyze this equation when there is no external perturbation, i.e., the measurand h[n] does not change from its initial value h[0]. Hence, Equation 13 simplifies to:

$$\phi[n] = -\delta \, \overline{ctr}[n] \frac{2\pi}{P_{ref}} + \phi[0] + \delta \, \overline{ctr}[0] \frac{2\pi}{P_{ref}}$$

$$= -\delta \, \overline{ctr}[n] \frac{2\pi}{P_{ref}} + \phi_{\text{initial}}.$$

(14)

For practical reasons the value of  $\delta$  will always be a small fraction of the

period  $P_{ref}$ , since the smaller its value, the higher the conversion gain of the DLL<sup>2</sup>. If  $\phi$  starts negative, the next value of  $\overline{ctr}$  will be decreased by 1, which will bring  $\phi$  closer to 0. On the other hand, if  $\phi$  starts positive, the next value of  $\overline{ctr}$  will be incremented by 1, also bringing the next value of  $\phi$  closer to 0. Regardless of the value of  $\phi_{initial}$ , the system will always converge to a state where the phase approaches 0 (as long as  $\delta < P_{ref}/2$ ). As explained before, the PD only generates two outcomes: ddl is either phase-advanced or phase-delayed in relation to sch. For this reason, after reaching equilibrium the value of  $\phi$  will have an oscillation between a slightly positive and a slightly negative value.

Therefore, when there is no external perturbation (f(h[n]) = f(h[0])) for all n), the system will always reach an stable equilibrium, as long as  $\delta < P_{ref}/2$ , and the M-bit counter does not saturate. The first condition is not a big concern, since we will usually wish the lowest  $\delta$  possible, and the second condition is achieved by properly designing the DCDL and the M-bit counter. The next important question to answer is: assuming that the delay caused by the sensing SAW-DL increases linearly  $(f(h[n]) = \alpha n)$ , what is the maximum slope  $\alpha$  in order for the system to remain locked?

To answer this question we start by rewriting Equation 2 in the form of a difference equation and then replace 10 and 11 into it:

$$\phi[n] = \phi[n-1] + \frac{2\pi}{P_{ref}} \left\{ \left[ f(h[n]) - f(h[n-1]) \right] - \delta \left[ \overline{ctr}[n] - \overline{ctr}[n-1] \right] \right\}.$$

(15)

The term f(h[n]) - f(h[n-1]) reduces to  $\alpha$ . Let us assume that  $\alpha$  is positive, and big enough so that the value of  $\overline{ctr}$  has to be increased at every cycle in order for the system to track this variations in the delay of the sensing SAW-DL. Therefore,  $\overline{ctr}[n] - \overline{ctr}[n-1]$  is 1, and Equation 15 simplifies to:

$$\phi[n] - \phi[n-1] = \frac{2\pi}{P_{ref}} (\alpha - \delta). \tag{16}$$

Let us take a look back in Figure 7. The delay in signal sch is increasing, which in turn causes an increase in  $\phi$ . However, the system will try to track the delay of sch by adding more delay to signal ddl. The system is kept locked if the phase  $\phi$  is kept below  $\pi$ . This means that the rate of variation in the

<sup>&</sup>lt;sup>2</sup>If  $\delta > P_{ref}/2$ , the system can jump from one stable equilibrium to another or even become unstable, specially when  $\delta > P_{ref}$ .

delay of *ddl* must be higher than the rate of variation in the delay of *sch*, which translates to a negative variation of  $\phi$ . Therefore:

$$\phi[n] - \phi[n-1] < 0$$

$$\frac{2\pi}{P_{ref}}(\alpha - \delta) < 0,$$

(17)

and the limit to the value of  $\alpha$  is:

$$\alpha < \delta$$

(18)

An analogous analysis can be made for a negative  $\alpha$ , which results in the condition  $\alpha > -\delta$ .

But what does the value of  $\alpha$  actually mean? The expression  $f(h[n]) = \alpha n$  translates to  $f(h(t)) = (\alpha/P_{clk})t$  in continuous-time. Therefore, the parameter  $\alpha/P_{clk}$  is the rate of variation in the delay caused by the sensing SAW-DL, in seconds-per-second. As a consequence of condition 18, the maximum value of this parameter is  $|\delta|/P_{clk}$ . We can increase it by speeding-up the system, i.e., making  $P_{clk}$  smaller. However, variations in the delay caused by the sensing SAW-DL will usually be extremelly slower than the rate of update of our system, and therefore the condition of Equation 18 is met without any speciall effort.

By giving enough time, respecting the conditions for the value of  $\delta$  and  $\alpha$ , and ensuring that the DCDL and the M-bit counter have the necessary tracking range, the system will keep track of the delay caused by the sensing SAW-DL. Since  $\alpha$  will usually be much lower than  $\delta$ , once the system reaches equilibrium the phase  $\phi$  will be kept close to 0. Therefore, we arrive to an expression for  $\overline{ctr}[n]$  from Equation 13:

$$\overline{ctr}[n] = \frac{f(h[n])}{\delta} + \frac{P_{ref}}{\delta 2\pi} \phi[0] - \frac{f(h[0])}{\delta} + \overline{ctr}[0]. \tag{19}$$

Hence, the value of  $\overline{ctr}[n]$  is directly proportional to the delay caused by the sensing SAW-DL (f(h[n])), and inversely proportional to the gain of the DCDL  $(\delta)$ .

To conclude, Equation 19 shows that the fully-digital DLL presented in Figure 6, under the right operating ranges, can be used to convert variations in the time-delay of a SAW-DL sensor into a digital word.

## 3 CMOS CONDITIONER FOR A SAW-DL HUMIDITY SENSOR

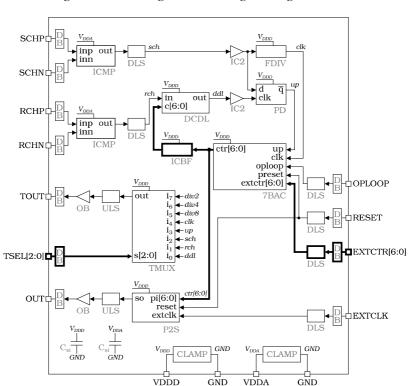

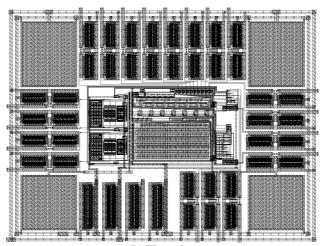

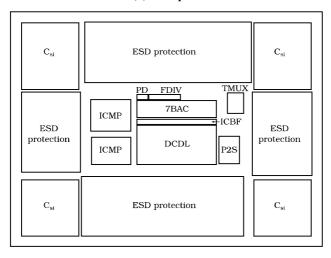

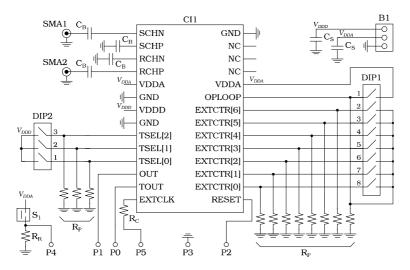

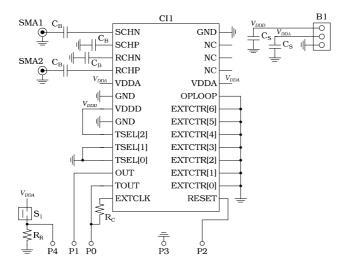

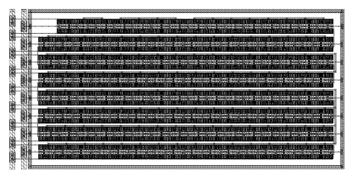

This chapter presents the design decisions, topologies, and the most relevant simulation results of each individual block, as well as the integration of the whole system. In order to transform the idea proposed in the last chapter into an actual integrated circuit with the desired functionalities, several decisions were made and restrictions were imposed. This led us to the block diagram of the system presented in Figure 10. This diagram is a complete representation of the fabricated IC.

Figure 10: Block diagram of the designed integrated circuit.

### 3.1 SYSTEM TOPOLOGY AND TECHNOLOGY

The blocks that compose the system are:

- DB, CLAMP: Diode bridge and power clamp, electrostatic discharge protection circuits;

- ICMP: Input Comparator;

- DLS: Down Level Shifter;

- IC2: Inverter Chain buffer of 2 levels;

- FDIV: Frequency Divider;

- DCDL: Digital-Controlled Delay Line;

- PD: Phase Detector

- ICBF: Inverter Chain Buffers;

- 7BAC: 7-bits Accumulator:

- OB: Output Buffer;

- ULS: Up Level Shifter;

- TMUX: Test Multiplexer;

- P2S: Parallel-to-Serial Converter:

- $C_{si}$ : Internal supply capacitors.

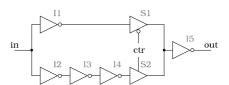

If we compare the DLL struture presented in Figure 6 and its actual implementation presented in Figure 10 we notice an additional block ICBF between the DCDL and the accumulator. Some of the **c**[6:0] inputs of the DCDL contain hundreds of gates, and therefore, the block ICBF serves to strengthen the signal ctr[6:0] before appling it to the DCDL. Moreover, this block helps to isolate ctr[6:0] from all the noise generated by the DCDL. Besides the buffers, a parallel-to-serial and a test multiplexer were added to the design. The former converts a parallel word of 8 bits into a serial data stream at a rate determined by an external clock signal applied to pin **EXTCLK**. The latter block allows us to measure 8 internal signals for testing and debugging purposes (div2, div4, and div8 are P2S internal signals).

The accumulator has two additional inputs: **oploop** and **extctr[6:0]**. The first one alows us to open the DLL loop by forcing the output **ctr[6:0]** of the accumulator to be equal to the external control word applied to **extctr[6:0]**. This function was included for testing purposes. By opening the loop and applying an external control word, we can measure the delay caused by the DCDL for each value of the word. Moreover, we can test whether the P2S is functioning properly or not by applying a known word to **extctr[6:0]**, and observing the output data stream in **OUT**.

The P2S outputs a data stream corresponding to a parallel word of 8 bits (1 byte). However, we chose to design the system with a control word of length 7 (ctr[6:0]), and let the last bit to a known level (low level, in this case). This known bit is used as a form of verifying that the parallel-to-serial conversion and the data acquisition are performed correctly. As we shall see in the next chapter, in the script we use to process the signal acquired in the output there is a verification of this last bit. If its value is not low, this is an indication that either the parallel-to-serial conversion or the data acquisition is incorrect.

The clk rate must be fast enough in order to track variation in the delay of the sensing channel. On the other hand, the clk period must be large enough in order to allow all internal signal to stabilize in the new state before computing the next state. We decided to divide the reference signal of 160 MHz by 32 in the frequency divider in order to meet these requirements.

The system is supplied with two voltage rails: 1.2 V, the core voltage labeled  $V_{DDD}$ , and 3.3 V, the IO voltage labeled  $V_{DDA}$ . We decided to use two voltage rails to have the internal blocks (the processing parts) built with faster and lower power devices, and the IO blocks built with devices less susceptible to ESD breakdowns<sup>1</sup>. The interface between these two voltage domains is accomplished through the level shifters. The DLS converts a digital signal from the IO voltage rail to the core rail. The ULS makes the opposite conversion. The signals applied to **TSEL[2:0]** were not shifted down. Fortunately, the protections were enough to prevent ESD breakdowns.

This project was designed in technology GF (Global Foundries) CMOS 130 nm, available through the educational program of MOSIS. We used two types of transistors: one for the core blocks, which has a minimum gate length of 120 nm and is supplied with 1.2 V ( $V_{DDD}$ ), and one for the IO blocks, which has a minimum gate length of 400 nm and is supplied with 3.3 V ( $V_{DDA}$ ). Both of them are standard devices and do not require any special fabrication step. We also make use of MIM (Metal-Insulator-Metal)

<sup>&</sup>lt;sup>1</sup>IO devices have a thicker oxide, which makes their breakdown voltage higher.

capacitors between the supply rails and ground in order to reduce the noise injected by the external supply sources. Integrated resistors are used in the ESD protection circuits as well as in the Input Comparators. There are 7 levels of metal available for routing signals and power. The 3 bottom-most metals are used for routing internal signals, and the 4 top-most metals for the power distribution network and for IO signals, except in some special cases.

### 3.2 ESD PROTECTION

The protection against electrostatic discharges (ESD) is of utmost importance in the design of integrated circuits. ESD events may happen during the fabrication and/or handling of the IC, and they can cause temporary or even permanent damages to the devices (GREASON; CASTLE, 1984). MOSFETs are susceptible to ESDs because of their capacitive nature. When a charge is induced in the gate of a MOSFET device, for instance due to contact to a charged human body or machine, a voltage proportional to this charge and inversely proportional to the gate capacitance is induced in the gate of the device. If this voltage is high enough, the dielectric that separates the gate from the bulk breaks, and an electric arc happens due to the high potential difference. This causes damage to the device. Moreover, as the CMOS technology scales down, so does the oxide thickness ( $t_{ox}$ ), which makes the devices even more susceptible to ESD events. Therefore, in our design we included circuits that provide a path to the induced charges in order to avoid ESD events.

The ESD protection structure used in all the **IO** pins is presented in Figure 11. The aim of using this structure is to prevent that charges induced between an **IO** pin and supply rails reach the gates of the transistors (internal circuitry) and, therefore, avoid ESD events. Under a normal operation of the system, the power clamp is an open circuit. However, when a steep transition in the voltage between **VDDA** and **GND** happens, the power clamp shorts these rails causing a high current leakage between them for a short period of time (controlled by the RC constant of the clamp). The diode bridge (DB) provides a path to the induced charges from the **IO** pin to the supply rails. The flow of currents happens as follow:

If a charge is induced in such a way that a positive voltage pulse appears

in IO with respect to VDDA, diode D<sub>1</sub> becomes forward biased, and a

current flows from IO to VDDA. This current significantly reduces the

amount of induced charges that reach the gates.

Figure 11: ESD protection structure for the IO pins.

• If a charge is induced in such a way that a negative voltage pulse appears in **IO** with respect to **GND**, diode  $D_2$  becomes forward biased, and a current flows from **IO** to **VDDA**. This current also significantly reduces the amount of induced charges that reach the gates.

Therefore, the diode bridge together with the power clamp provide a path to charges induced between the IO and the supply pins.

The resistor  $R_{DB}$  provides a path with higher impedance to the induced charges, in order to force them to flow through  $D_1$ ,  $D_2$ , and the power clamp. There is a second path through  $D_3$  and  $D_4$  for the charges that cross  $R_{DB}$ , in order to increase the ESD protection of the internal circuitry. The higher the value of  $R_{DB}$ , the better the protection. However, this resistance influences the performance of the system, since it attenuates the signals flowing in and out of the IC. We set this resistance to 1.1 k $\Omega$ . When measuring the outputs of the system, we will use a voltage probe with 15 pF of capacitance. This ESD protection resistance and the voltage probe capacitance create a low-pass filter with a cut-off frequency of 9.6 MHz, around two times higher than the maximum frequency we wish to measure (5 MHz, the internal clock signal). Therefore, the ESD structure will not prevent the correct measurement of the output signals, though it will attenuate its harmonics. On the other hand, the input signals that come from the SAW-DL have a frequency of 160 MHz. Thus, the ESD structure has to be considered in the design and simulation of the input comparators.

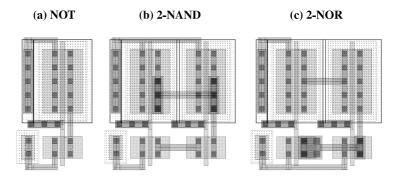

## 3.3 DIGITAL LIBRARY

Except for the input comparators and the level shifters, the system is entirely composed of standard logic gates and registers. Therefore, the first part in the design was to create a digital library with the schematic and layout views of all the digital circuits necessary for the other blocks. These circuits are all supplied with the core voltage  $V_{DDD} = 1.2 \text{ V}$ , except for the IO inverters,

which are supplied with  $V_{DDA} = 3.3 \text{ V}$ .

## 3.3.1 Combinational Logic

The design criteria for the core inverter, which uses 1v2 devices, were:

- Minimum gate length: to reduce power consumption, and the propagation delay;